近日,集成電路學(xué)院童喬凌教授和閔閏副教授團隊在功率開關(guān)驅(qū)動領(lǐng)域的最新研究成果以“An Adaptive Three-stage GaN Gate Driver with Peak Miller Plateau Voltage Tracking and Voltage Tailing Suppression For 36.4% Switching Loss Reduction”為題,被集成電路設(shè)計領(lǐng)域頂級期刊IEEE Journal of Solid-State Circuits (JSSC)接收。

隨著數(shù)據(jù)中心、AI服務(wù)器及便攜設(shè)備對電源功率密度要求日益提高,GaN功率器件因開關(guān)速度快、體積小等優(yōu)勢成為高頻電源核心。然而,傳統(tǒng)驅(qū)動方案存在兩大瓶頸:1、米勒平臺階段啟動延遲:初始電壓變化率(dv/dt)過低,導(dǎo)致開關(guān)損耗增加;2、電壓拖尾效應(yīng):開關(guān)末期dv/dt驟降,延長電壓電流重疊時間。

針對GaN功率器件驅(qū)動瓶頸,團隊設(shè)計了一款自適應(yīng)三段式有源門極驅(qū)動芯片,為高密度電源系統(tǒng)能效提升提供關(guān)鍵技術(shù)支撐。

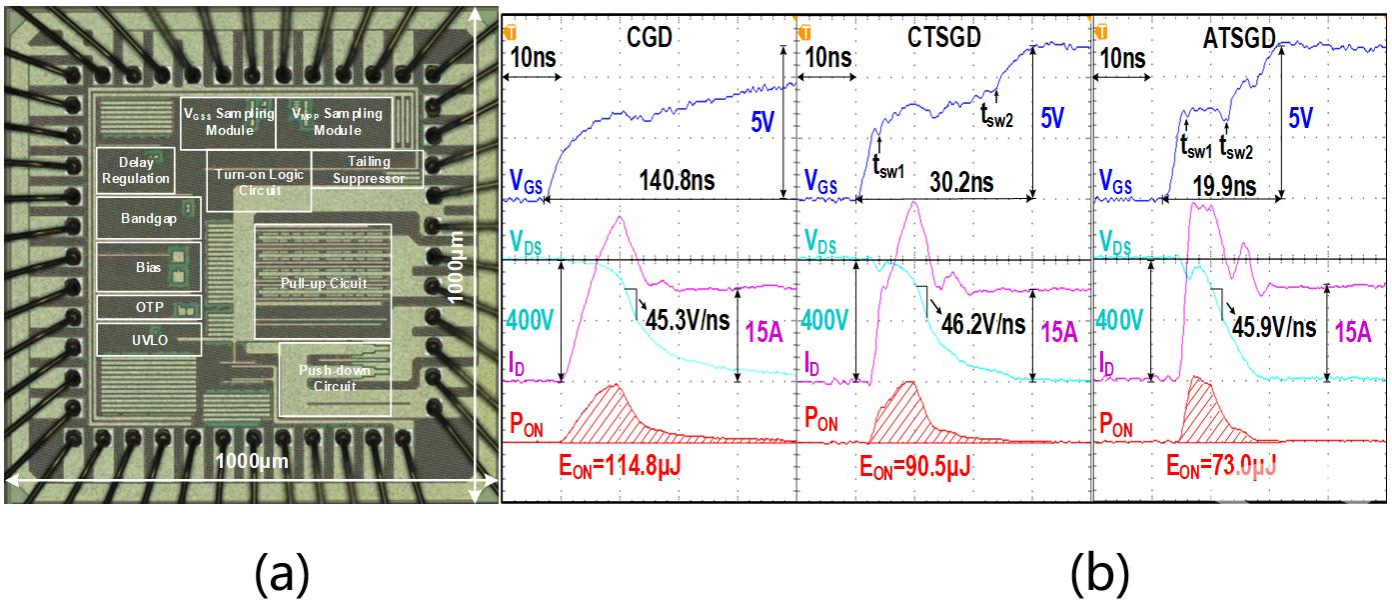

圖1驅(qū)動芯片架構(gòu)

圖2(a)芯片照片(b)雙脈沖測試結(jié)果

該芯片采用了三大創(chuàng)新設(shè)計:1、三段動態(tài)電流控制:在米勒平臺期智能切換驅(qū)動電流,使dv/dt近乎恒定;2、米勒平臺跨周期追蹤技術(shù):實時追蹤米勒平臺峰值電壓,動態(tài)優(yōu)化電流切換點,解決負載波動導(dǎo)致的啟動延遲問題(降低慢啟動損耗46.1%);3、快速拖尾抑制技術(shù):基于柵極電壓突降檢測電壓拖尾起始點,精準觸發(fā)大電流加速關(guān)斷(降低拖尾損耗88.7%)。

芯片基于0.18μm BCD工藝制造。在400V/15A嚴苛測試中,dv/dt峰值在全開關(guān)過程中保持在45V/ns,單次開關(guān)損耗從114.8μJ降至73.0μJ。這是已報道GaN驅(qū)動芯片的最高能效紀錄。

集成電路學(xué)院童喬凌教授和閔閏副教授主要從事高功率密度電源專用芯片技術(shù)研究,共主持國家級縱向項目11項,主持企業(yè)橫向項目40余項。近五年發(fā)表中科院一區(qū)期刊論文20余篇(JSSC、TPEL、TIE、TII等)。設(shè)計的SiC驅(qū)動與脈沖電源被用于“天琴一號”型號任務(wù),助力我國掌握“無拖曳控制”(世界唯二)。設(shè)計的車規(guī)級高邊開關(guān)驅(qū)動芯片先后通過AEC Q-100可靠性測試和冬季路測,在東風(fēng)汽車量產(chǎn)裝車(猛士、風(fēng)神、奕派)